本文涉及印刷电子产品和PCB。我获得了从事PCB设计的带宽设计技术,后来将相同的原理应用于印刷电子设计。在本文中,我将解释我对带宽的了解,以及如何将其应用于PCB和印刷电子产品。

在详细介绍带宽之前,我认为有必要重新审视我们在电子领域中“信号”一词的含义。至少对我而言,最容易理解如下“信号”:信号是包含信息的电量。通常,所涉及的电量是“电压”,而包含的信息是“电压水平随时间的变化”。我们有兴趣了解特定时间的确切电压水平。例如,数字信号信息是逻辑0和1状态的队列,只有在正确的时间检测到正确的逻辑电平时,我们才能获得正确的信息。从电子学的角度来看,信息为0或1,如果我们丢失任何脉冲,那么我们就会丢失信息。模拟信号没有区别:在特定时间的特定电压会生成信息。如果我们的电子设备(例如削波)导致模拟信号失真,那么我们将丢失信息。信号信息对于可靠的产品操作是必不可少的,有时可能需要以音频或视觉反馈的形式向最终用户提供信息。

当通过从时域到频域的傅立叶变换来计算信号时,信号可能包含几个频率分量。时域信号是所有包含的频率分量的总和,信号的形状取决于每个单独频率的功率电平。数字信号包含一个DC分量,然后是许多强度较低的AC分量,其强度随频率的增加而降低。更快的信号意味着更高的频率分量。这些交流频率中的每一个都是一个非常窄的频带,即单频正弦波信号。因此,数字信号是直流信号加上大量正弦波信号的总和。纯AC信号可以是窄带(如正弦波),因为它们不包含DC分量。

信号信息位于频率范围内的某处,而该信息所需的所有频率分量都决定了带宽。带宽之外的频率是不必要的,并且可以被拒绝,例如通过过滤,因为这些频率不携带信号的附加信息。带宽可以被认为是电信号的工作区域,在该区域中它不会丢失信息,并且也是信号的电路径(即走线)或负载所必需的。然后对电子设备进行相应的设计,并且在最佳情况下,当信号馈入走线时,保持不变。如果信号速度高于走线或滤波器的带宽,则会修改信号,这通常意味着某些频率分量会被滤除。跟踪本身将具有带宽限制,

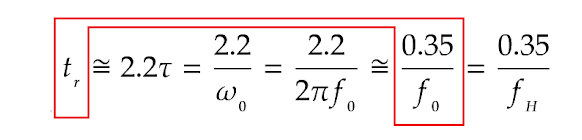

信号的带宽由信号上升时间(10%到90%)要求决定,可以通过以下经验法则表示:

带宽= 0.35 / tr(1)

信号频率并不像上升时间要求那么重要,仅仅是因为信号不同。即使信号频率完全相同,数字信号(占空比为50%)与PWM信号(占空比为10%至90%)的上升和下降时间要求也不同。在PWM信号中,当信号“开”状态比“关”状态(90%)短(占空比为10%)时,这意味着与较长的“开”状态脉冲相比,上升时间必须快得多。当然,信号频率也很重要,因为频率越高,其上升时间就需要越快。这种带宽经验法则是我用于信号带宽相关设计任务的第一工具。我是很久以前从我大学的电子设计讲师那里学到的,从那以后,我就在设计中多次使用了它。

图1。信号上升时间与带宽之间的关系(2)

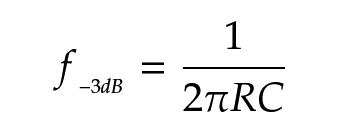

我曾经将模拟和数字信号的速度限制在所需的最小带宽内,这可以通过滤波器轻松完成。RC滤波器是最简单的滤波器之一,它易于实现且易于设计。对于RC滤波器,-3dB截止频率的计算公式为:

RC滤波器的截止频率(3)

其中R是串联电阻,C是电阻之后接地的电容。原理图实现在下面的图2中给出。

图2. RC滤波器的原理图实现

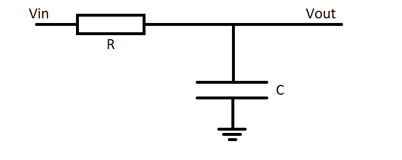

您必须记住,如果您选择的RC滤波器电阻与信号驱动器的输出电阻大约处于相同的欧姆水平,那么在计算-3dB截止频率时也必须考虑到输出电阻。RC滤波器的计算公式为:

具有输出电阻的信号驱动器上RC滤波器的截止频率

带宽可以认为与-3dB截止频率相同。截止频率表示此时的频率已衰减至其原始功率水平的一半。也可以使用其他滤波器,例如,许多MCU都包含一个用于GPIO上升和下降时间的压摆率限制器。此功能产生与过滤器相同的结果,但是可以由软件控制,不需要其他组件。过滤信号的原因基本上有两个:1)我想最小化该特定信号的整体噪声水平,以及2)我想最小化由于串扰引起的耦合干扰。当然,通过最佳的PCB叠层设计来最小化串扰是有意义的,但是滤波器为我们提供了另一个将其最小化的工具。

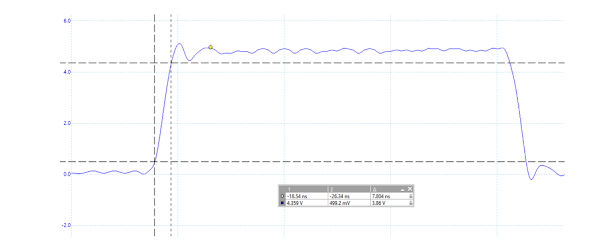

下图显示了示波器对3MHz数字信号脉冲的测量,带和不带滤波。图3是一个“未经滤波”的信号,其速度仅受信号驱动器输出电阻Rs和负载电容的限制,测得的上升时间为7.8ns。我们不知道确切的负载电容,但是根据该信号驱动的组件的数据手册,有一个反向接地的保护二极管,通常这些电容的电容约为10pF。但是,在这种情况下,准确的电容值并不重要,因为根据经验法则,带宽现在为0.35 / 7.8ns = 44.9MHz,我们可以对其进行相当多的滤波而不会丢失信号信息。增加的滤波电容将比二极管电容高得多。

图3. 3MHz信号,未经滤波

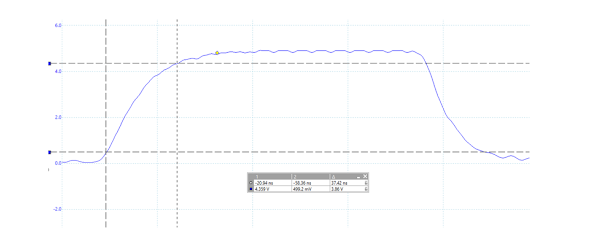

图4显示了相同的信号,但由RC滤波器滤波。我选择了100Ω电阻器和100pF电容器,此外,我们还测量了信号驱动器的38Ω输出电阻和〜10pF IC负载电容,这些都必须考虑在内。RC滤波器计算器显示的截止频率为:

f-3dB = 1/2π(100Ω + 38Ω)*(100pF + 10pF) = 10.484MHz

根据带宽计算,该带宽的最快上升时间为0.35 / 10.484MHz = 33.4ns。从图4中我们可以看到,测得的上升时间为37.4ns,在这种情况下,它足够接近计算值。通常,我并不期望计算值和测量值之间有完美的匹配,但是通常我会通过快速计算来检查结果,以确定结果是否足够接近应用程序的要求。大多数情况下,我设计的过滤器不在边缘,但是足够有效并且有足够的余量。

图4.带RC滤波器的3MHz信号

该信号是数字信号,从形状上我们可以看到,滤波后我们没有丢失信息。我们仍然可以可靠地将脉冲检测为逻辑1,并且在下一个周期开始之前,信号仍然足够快地进入低态。此外,由于高频谐波已被衰减,因此噪音少得多。通过这种方法,我成功地减少了数字总线走线与敏感传感器走线之间的串扰,并使传感器正常工作而无需重新布线。这是通过仅过滤产生干扰的信号而完全不接触模拟信号来实现的,因为传感器带宽要求高于数字总线。

在印刷电子产品中,将带宽限制在适当的水平甚至比在PCB中更为重要。限制印刷电子设备中带宽的主要原因是为了减少由于串扰引起的干扰。通过在阻抗和串扰方面建立最佳的堆叠,印刷电子产品受到的限制更大,我需要使用滤波器或压摆率受限的信号。当我们考虑印刷电子设备的堆叠时,我们可以看到彼此交叉的走线仅被局部薄的印刷介电层隔开。它的厚度只有几十微米,这意味着交叉走线之间的电容耦合非常强。迹线之间的电容取决于交叉区域和两者之间的介电层厚度。在印刷电子产品中,走线往往比在PCB中宽,S和介电层比PCB中的薄得多,这导致走线之间的电容也更大。更大的电容意味着更低的频率通过该“电容”耦合。除此之外,布局区域的尺寸可能与产品尺寸几乎相同,这意味着走线的长度很长,从而增加了走线的电感。与较高的电容一样,较高的电感会影响较低的频率。

由于涉及各种材料和堆叠,印刷电子产品带来了低频带宽挑战,但通过广泛用于PCB设计的已知原理和方法可以解决这些问题。另外,对带宽的理解在印刷电子设计中很重要,需要仔细考虑。由于材料差异,印刷电子产品中与信号速度相关的挑战与PCB中的挑战相似,但在印刷电子产品中,我们面临的挑战可能要少得多。就个人而言,因此,我在原理图中写下了关键信号频率,以提醒自己它们很重要,如果我注意到潜在的问题,则会将带宽限制在所需的最低水平。

下一页:无铅PCBA加工的分步过程